# REX3 Specification

Mark Goudy Rick Jeng Eric Linstadt Mukesh Patel Adrian Sfarti Bob Sherburne

Silicon Graphics, Inc.

**Revision 1.0**

| 1:             | Introduction                                        |        | •   |      |    |     | •  |     |      |   | • |   |   |   |   | . 5      |

|----------------|-----------------------------------------------------|--------|-----|------|----|-----|----|-----|------|---|---|---|---|---|---|----------|

|                | 1.1: Part Name and Number.                          |        |     |      |    |     |    |     |      |   |   |   |   |   |   | . 5      |

|                | 1.2: General Description                            |        |     |      |    |     |    |     |      |   |   |   |   |   |   | . 5      |

|                | 1.3: Features                                       |        |     |      |    |     |    |     |      |   |   |   |   |   |   | . 5      |

|                | 1.4: Newport Architecture.                          |        |     |      |    |     |    |     |      |   |   |   |   |   |   | . 6      |

|                | 1.5: REX3 Architecture .                            |        |     |      |    |     |    |     |      |   |   |   |   |   |   |          |

|                | 1.6: Performance                                    |        |     |      |    |     |    |     |      |   |   |   |   |   |   |          |

|                |                                                     |        |     |      |    |     |    |     |      |   |   |   |   |   |   |          |

| 2:             | Device Interface                                    |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 11       |

|                | 2.1: Pin Diagram                                    |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 11       |

|                | 2.2: Pin Descriptions                               |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 12       |

|                | 2.3: VHDL Description                               |        | •   |      | •  | •   | •  |     |      | • | • |   |   |   | • | 14       |

|                | 2.4: Package Pin Assignment                         |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 15       |

| <del>ر</del> . | Programmer Interface                                |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 20       |

| 0.             | 3.1: Registers                                      |        |     |      |    |     |    |     |      |   |   |   |   |   | • | 20       |

|                | 3.1.1: Control Register Bit                         |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 20       |

|                | 3.1.1.1: DRAWMODE                                   |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 23<br>23 |

|                | 3.1.1.2: DRAWMODE                                   | 1 Re   | gis | ter. |    |     |    | :   |      |   |   |   | ÷ | ÷ | ÷ | 25       |

|                | 3.1.1.3: LSMODE Reg                                 | jistei | r.  |      |    |     |    |     |      |   |   |   |   |   |   | 27       |

|                | 3.1.1.4: CLIPMODE R                                 | egis   | ter |      |    | •   | ·  | •   |      |   |   |   |   |   | • | 27       |

|                | 3.1.1.5: STATUS Reg                                 | ister, | /US | SER_ | ST | ATU | SR | egi | ster | • | • | · | · | · | · | 27       |

|                | 3.1.1.6: CONFIG Regi<br>3.1.1.7: DCBMODE R          | ster   | tor | • •  | •  | •   | •  | •   | • •  | • | • | · | · | · | • | 28<br>29 |

|                | 3.2: Coordinate System                              |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 30       |

|                | 3.3: Clipping and Masking                           |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 30<br>30 |

|                | 3.4: Iterator Overview                              |        |     |      |    |     |    |     |      |   |   |   |   |   | • | 30<br>31 |

|                |                                                     |        |     |      |    |     |    |     |      |   |   |   |   |   | • |          |

|                | 3.5: Framebuffer Access Mode                        |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 32       |

|                | 3.5.1: Lines: Overview .<br>3.5.1.1: Line Draw or I |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 32<br>32 |

|                | 3.5.1.2: Line Draw: Se                              |        |     |      |    |     |    |     |      |   |   |   |   |   |   |          |

|                | 3.5.1.3: Line Draw:                                 |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 33       |

|                | 3.5.2: Point Draw or Read                           |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 33       |

|                | 3.5.3: Spans: Overview .                            |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 33       |

|                | 3.5.3.1: Span Draw or                               |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 33       |

|                | 3.5.3.2: Span Draw: S                               |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 34       |

|                | 3.5.3.3: Span Draw or                               |        |     |      |    |     |    |     |      |   |   |   |   |   | · | 34       |

|                | 3.5.4: Blocks: Overview.                            |        |     |      |    |     |    |     |      |   |   |   |   |   | • | 34       |

|                | 3.5.4.1: Block Draw or                              |        |     |      |    | -   |    |     |      |   |   |   |   |   | · | 34<br>25 |

|                | 3.5.4.2: Block Draw: \$<br>3.5.4.3: Block Draw or   |        |     |      |    |     |    |     |      |   |   |   |   |   | • | 35<br>35 |

|                | 3.5.4.4: Block Draw of                              |        |     |      |    |     |    |     |      |   |   | ÷ | ÷ | ÷ | ÷ | 35       |

|                | 3.5.5: Fast Clear                                   |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 35       |

|                | 3.5.6: Screen-to-Screen M                           |        |     |      |    |     |    |     |      |   |   |   |   |   |   | 36       |

|                | 3.6: Line Draw Instructions.                        |        |     |      |    |     |    |     |      |   |   |   |   |   |   |          |

|                |                                                     | -      | -   | • •  | -  | •   | -  | -   |      | - | - | - | • | - | - |          |

| 3              | Bresenham A<br>6.1.1: I_line(x1<br>6.1.2: F_Line(x1 | 1,y1,x2,y2 | 2,SK | IPL  | AS  | T,S | SKIF | PFIF | RST   | ).  |    |   |   |   |   |   | 37         |

|----------------|-----------------------------------------------------|------------|------|------|-----|-----|------|------|-------|-----|----|---|---|---|---|---|------------|

|                | Bresenham A<br>6.2.1: A_Line(                       |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 39<br>39   |

|                | 6.2.2: A_Edge                                       |            | y1,x | 2,y  | 2,e | 1,a | a_ta | able |       | IP- |    |   |   |   |   |   | 40         |

| 3              | 6.2.3: A_Edge                                       |            | x1,y | /1,x | 2,y | 2,e | 1,a  | a_ta | able, | SKI | P- |   |   |   |   |   | 40         |

| 3.7. Dout      | ble Buffering .                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | nebuffer Data V                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | Patterning and                                      |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | Dither                                              |            | -    |      |     |     |      |      |       |     |    |   |   |   |   |   | -          |

|                | 8.2.1: RGB Di                                       |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | 8.2.2: Color In                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

| 3.8.3:         | Color rounding                                      | g          |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 74         |

| 3.8.4:         | Logic OP .                                          | -<br>      |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 74         |

|                | Blend                                               |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | ebuffer Format                                      |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | mebuffer PIO a                                      |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | O Management                                        |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | ntext Switching                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | play Control Bu                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | p Reset and Ini                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | -                                                   |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

| 4: System Int  | erface                                              |            | •    |      |     | •   |      | •    |       |     | •  |   | • | • |   |   | 84         |

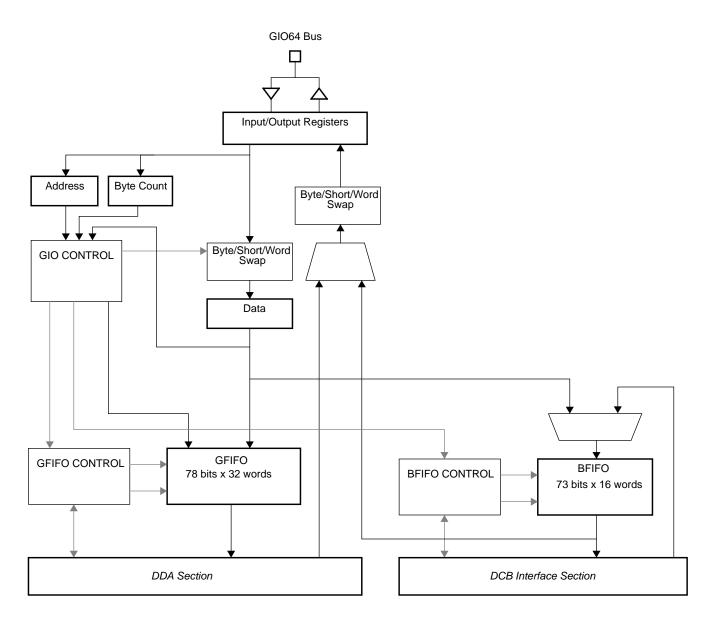

| 4.1: GIO       | 64 Bus Interface                                    | э          |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 84         |

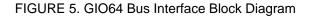

| 4.2: Disp      | lay Control Bus                                     | Interface  | ).   |      |     | •   |      |      |       |     | •  |   | • |   |   |   | 84         |

| 4.3: VRA       | M Interface .                                       |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 86         |

| 4.4: Test      | er Interface .                                      |            | •    | •    | •   | •   | •    | •    |       |     | •  | • | • | • | • |   | 104        |

| 5: Architectur | al Description                                      |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 108        |

| 5.1: GIO       | 64 Bus Interface                                    | э          |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 108        |

|                | lay Control Bus                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

| •              | Unit                                                |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

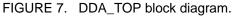

|                | DDA_TOP Po                                          |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

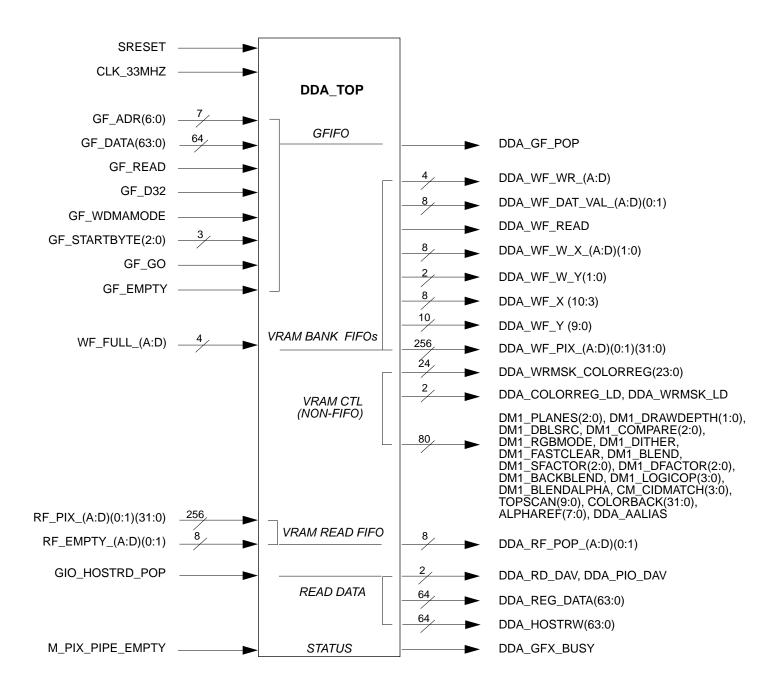

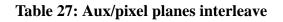

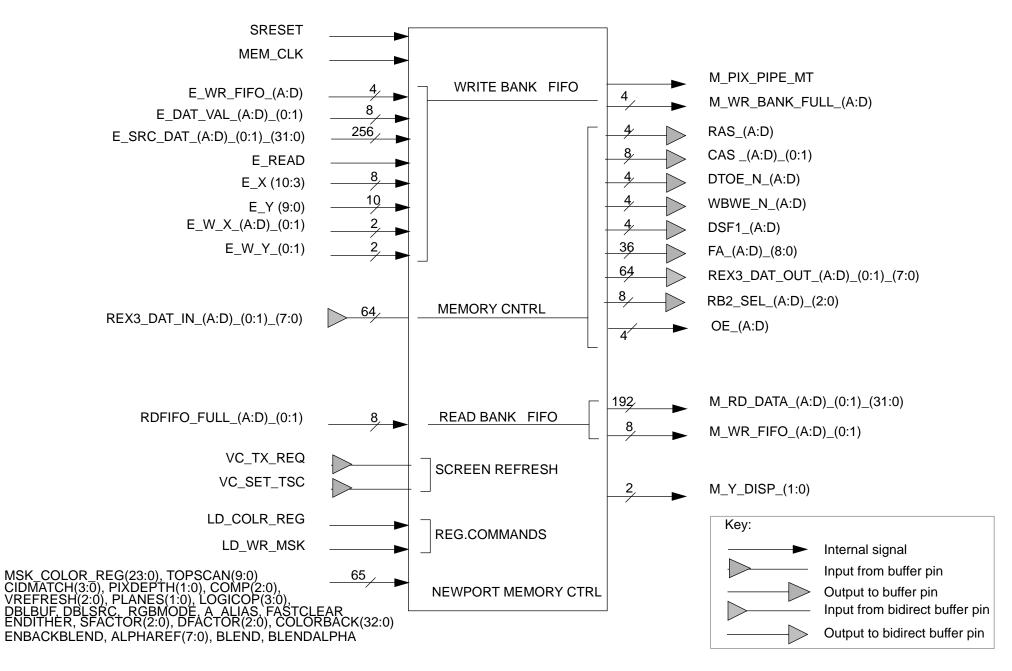

|                | M Controller Ur                                     |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 114        |

| -              | Vram Interleav                                      |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 114        |

|                | 4.1.1: Aux/Pix                                      |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 114        |

| 5              | 4.1.2: Writema                                      | ask        |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 115        |

|                | Vram address                                        | -          |      |      |     |     |      |      |       |     |    |   |   |   |   |   | 115        |

|                | 4.2.1: Pixel pla                                    |            |      |      |     |     |      |      |       |     |    |   |   |   | • | · | 115        |

|                | 4.2.2: Aux plai<br>4.2.3: Row add                   |            |      |      |     |     |      |      |       |     |    |   |   |   | · | · | 115<br>115 |

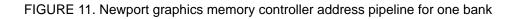

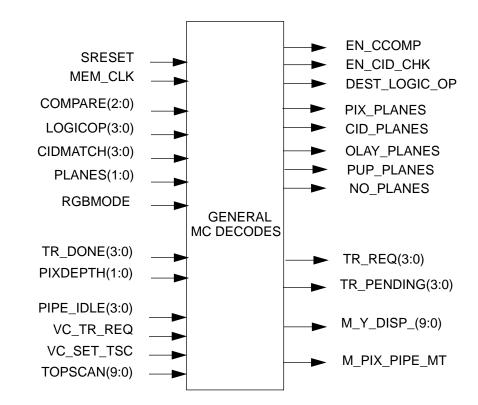

|                | Memory Conti                                        |            |      |      |     |     |      |      |       |     |    |   |   |   |   | • |            |

|                | •                                                   |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

|                | VRAMS                                               |            |      |      |     |     |      |      |       |     |    |   |   |   |   |   |            |

| 5.4: Scar      | Refresh Laten                                       | су         | •    | •    | •   | •   | •    | •    |       | •   | •  | • | • | • | • | • | 121        |

|    |                  | General de  |         |       |     |      |     |     |    |   |   |   |   |   |   |   |     |

|----|------------------|-------------|---------|-------|-----|------|-----|-----|----|---|---|---|---|---|---|---|-----|

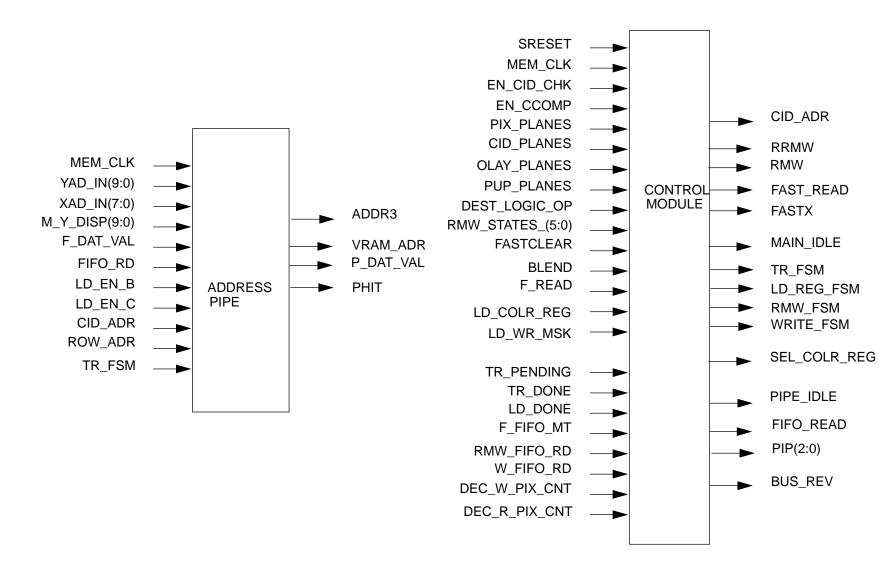

|    | 5.4.0.2:         | Control mo  | odule.  |       |     |      |     |     |    |   |   |   |   |   |   |   | 132 |

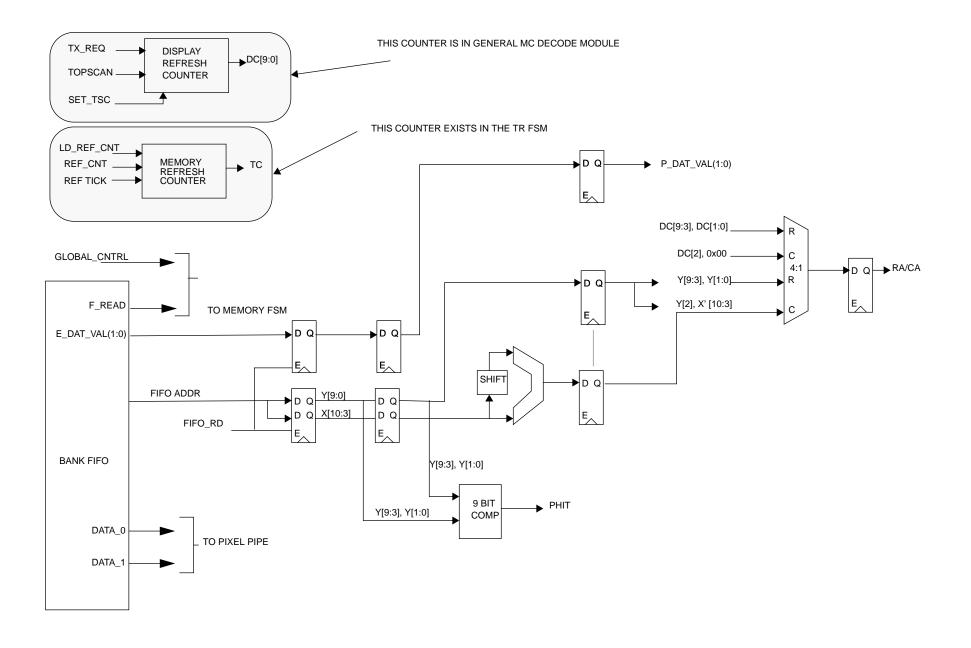

|    | 5.4.0.3:         | Address P   | ipe .   |       |     |      |     |     |    |   |   |   |   |   |   |   | 133 |

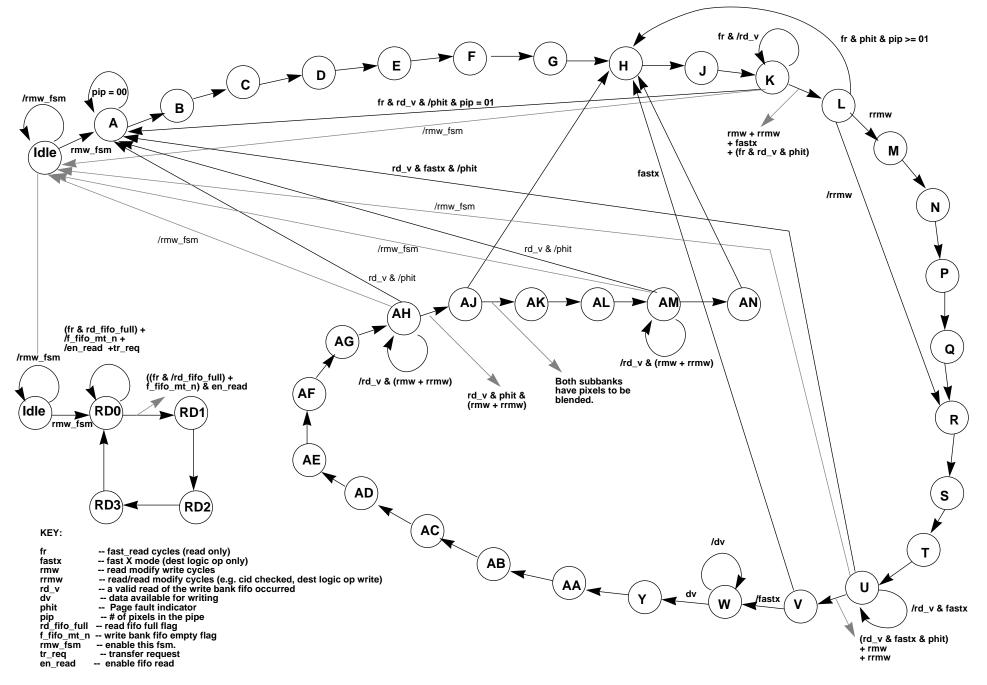

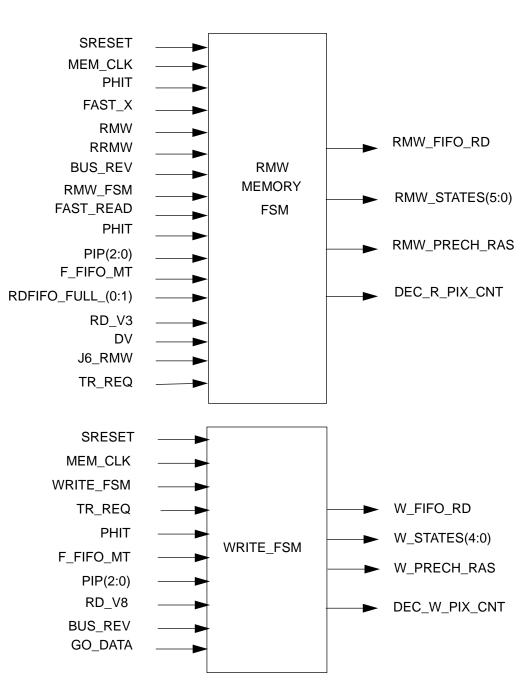

|    | 5.4.0.4:         | RMW state   | e mac   | hine  |     |      |     |     |    |   |   |   |   |   |   |   | 134 |

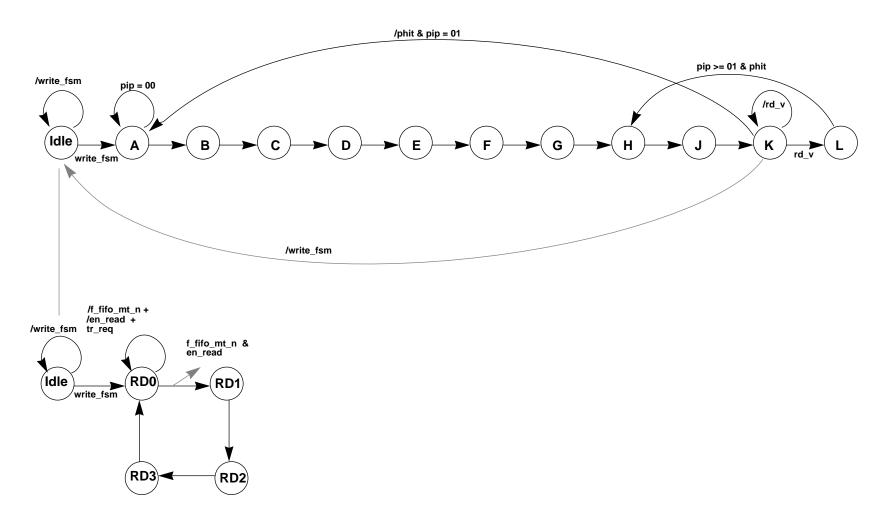

|    | 5.4.0.5:         | Write state | mach    | nine  |     |      |     |     |    |   |   |   |   |   |   |   | 135 |

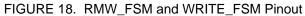

|    | 5.4.0.6:         | Load regis  | ters s  | tate  | ma  | chir | ne  |     |    |   |   |   |   |   |   |   | 136 |

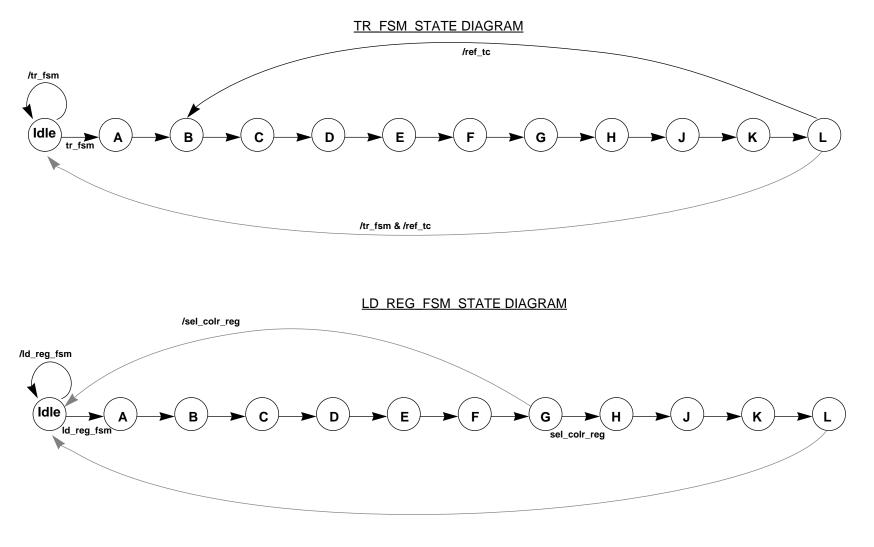

|    | 5.4.0.7:         | Refresh .   |         |       |     |      |     |     |    |   |   |   |   |   |   |   | 137 |

|    | 5.4.0.8:         | Out block   | modul   | е.    |     |      |     |     |    |   |   |   |   |   |   | • | 139 |

|    | 5.4.1: Gate      | Count       |         |       | •   |      |     |     |    |   |   |   |   |   |   |   | 140 |

|    | 5.4.3: Pixel     | Processing  | Pipe    |       |     |      |     |     |    |   |   |   |   |   |   |   | 141 |

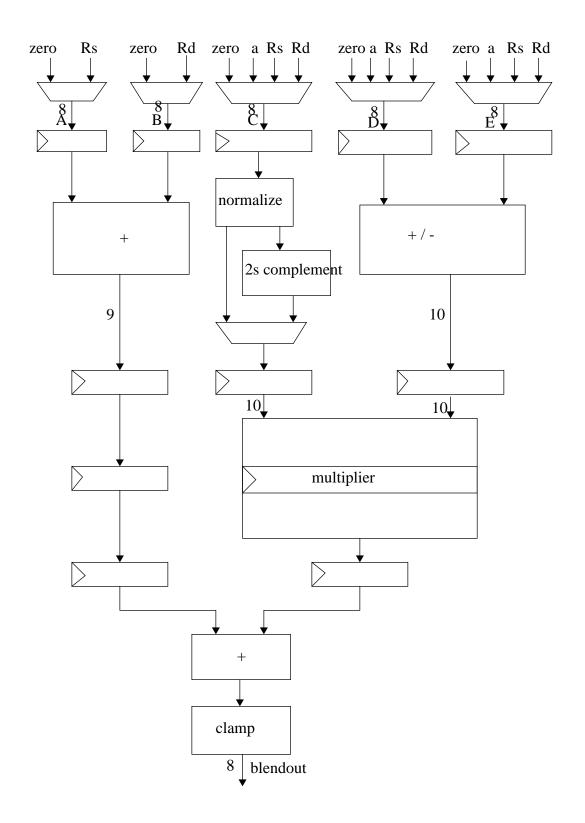

|    | 5.4.3.1:         | Blender .   |         |       |     |      |     |     |    |   |   |   |   |   |   |   | 141 |

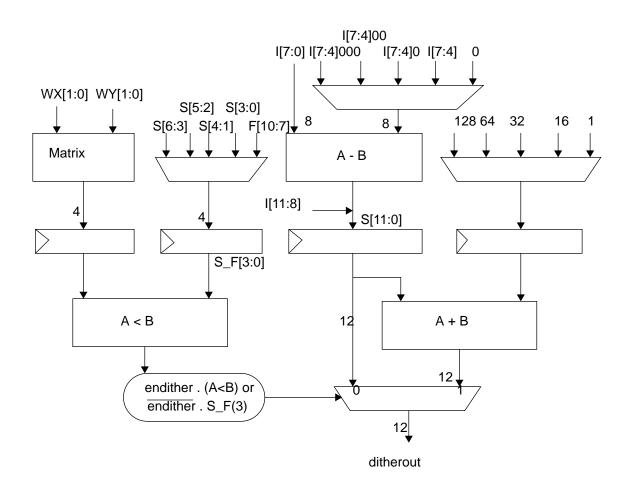

|    | 5.4.3.2:         | Dithering.  |         |       |     |      |     |     |    |   |   |   |   |   |   |   | 144 |

|    | 5.4.3.3:         | Gate coun   | t of pi | xel p | roc | ess  | ing | pip | be | • | • | • | • | • | • | • | 145 |

| 6: | Revision History |             |         |       |     |      |     |     |    |   |   |   |   |   |   |   | 146 |

# 1 Introduction

This document describes the REX3, part of the Newport ("the least graphics you'll ever need") graphics subsystem.

### 1.1 Part Name and Number

Part Name: REX3 SGI Part Number: 099-9005-001 Vendor: LSI Logic Corporation Vendor Part Number: L1A9040 Technology: LC300K (0.6 micron CMOS gate array) Base Wafer: L300415P Package: 304 MQUAD Gate Count:149,000 equivalent gates, including 5.7K bits dual port RAM.

### 1.2 General Description

REX3 is the raster engine for Newport graphics. The basic operation of the raster engine is to draw lines and spans. Various packed formats of host DMA are also supported. It is based on some of the concepts of REX1, i.e there is no dedicated geometry engine for graphics. Instead, the hosts floating point unit is used as the geometry engine. Like REX1, Z buffering is done by the host in system memory. REX3's register interface has been optimized for minimum host writes to execute primitives. REX3 has various pixel formats to accommodate a low cost 8 bits/pixel system as well as a 24 bits/pixel system. Besides the pixel planes REX3 supports CID, PUP and Overlay planes. Also, in order to achieve high frame buffer writing bandwidth, the frame buffer is architected as an 8 way interleave combined with a Y axis interleave. There are two sets of RGBA iterators so 2 shaded pixels/clock are generated. For flat filled spans, four pixels/clock are generated. In order to bound the package size to less than 304 pins, the frame buffer data is byte serialized for each of the eight interleaves. This data is deserialized by RB2s' before writing to the frame buffer. In order to limit the number of gates in REX3, the read/write formaters and the logicop functions have been incorporated into RB2s.

### 1.3 Features

- 33 MHz GIO64 Bus Interface

- 66 MHz Isotropic 8 way interleaved frame Buffer Interface

- 33MHz Display Bus Interface with synchronous / asynchronous / burst mode slave support

- Bresenham line iterators

- RGB and CI anti-aliased Bresenham lines

- Bi-endian support

- Software Z buffer

- Blend function

- 1280 x 1024 resolution

- Upto 76Hz screen refresh

- Upgradable from 8 pixel + 2PUP + 2CID planes to 24 pixel + 8 Overlay(or 4+4) + 2PUP + 2CID planes

- Optional Express Video ready

GenLock capability

### 1.4 Newport Architecture

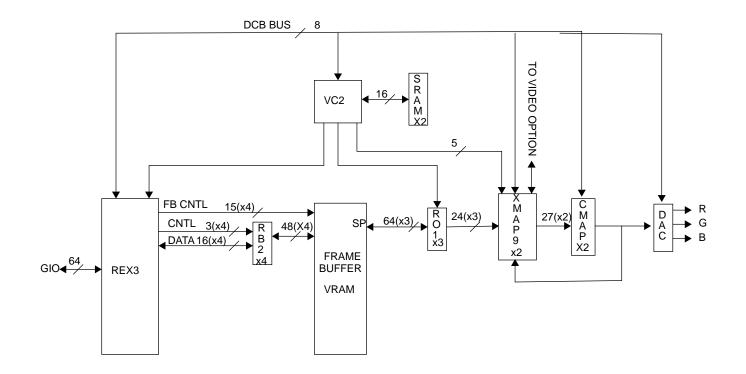

Newport graphics is made of the following major components:

- 1. REX3

- 2. RB2

- 3. Frame buffer

- 4. RO1

- 5. XMAP9

- 6. CMAP

- 7. VC2

- 8. RAMDAC

- 9. Static Ram

The graphics pipeline begins with the host writing into the REX3 registers to execute primitives. REX3 transforms these primitives into screen coordinates and writes the data via RB2 into the frame buffer. The frame buffer is made of Vrams (2MBit) in an 8 way interleave configuration. The serial ports of the frame buffer are read into RO1 and passed into XMAP9 which manipulates the data for multi mode screen. XMAP9 passes the data onto the CMAP which consists of high speed static ram for Color Index modes. When in RGB mode, the data goes through other static ram within CMAP that is normally linearly mapped, although for image processing applications it does not have to be linearly mapped. The output of CMAP is fed into the RAMDAC for display to the screen. The gamma correction tables reside in the RAMDAC. The output of the CMAPs is also fed back to XMAP9 and output onto the Video port. Video data can also be accepted from the video port and output to the CMAP to display on the graphics monitor. VC2 provides all the relevant timing for the graphics sub system.

A block diagram of the Newport graphics sub-system is shown in Figure 1.

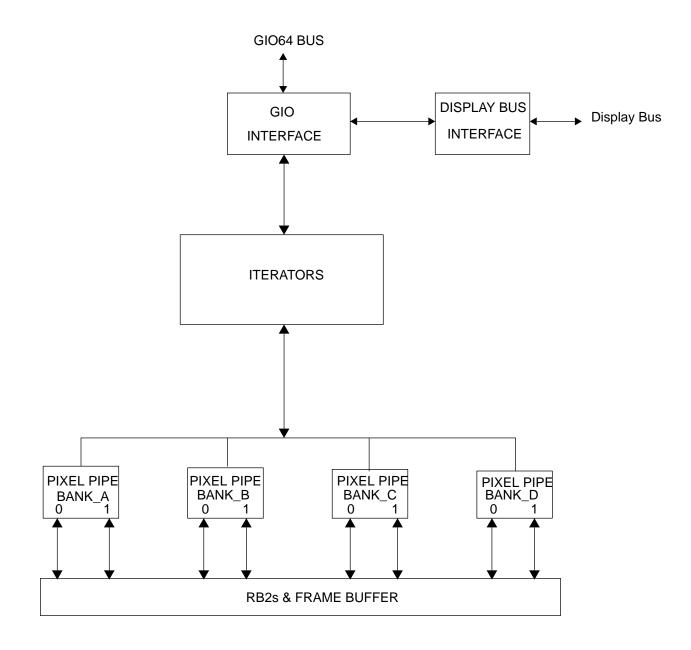

### 1.5 REX3 Architecture

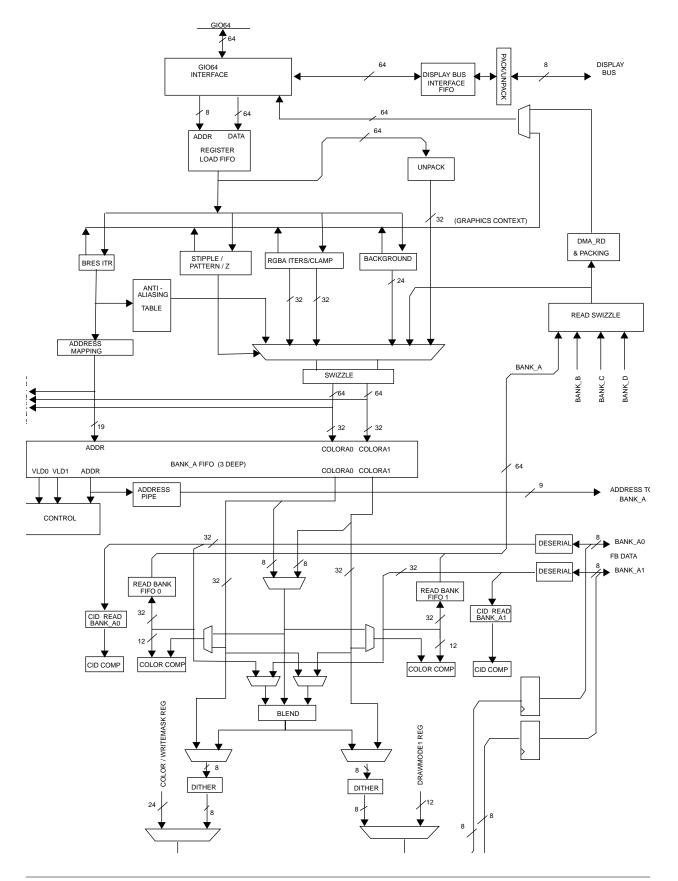

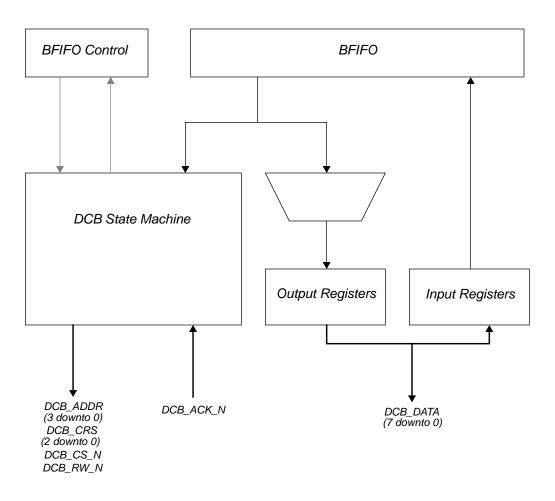

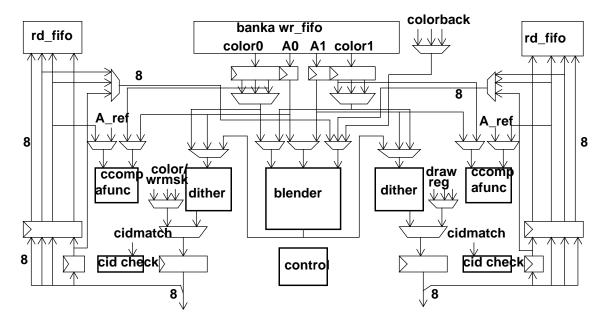

Figure 2 shows the top level block diagram of REX3. REX3 could be viewed as three logical blocks. The first block, which interface to the host bus (GIO64) is the GIO block. REX3 supports both GIO64 and GIO32 protocol, the default being GIO64. The GIO64 bus may be either 64 or 32 bits wide. This block receives commands for all the primitives that REX3 draws as well as provide host access to other devices in the display and video (optional) subsystems. REX3 is implemented as a GIO64 bus slave which decodes addresses on the GIO64 bus to detect accesses to its own registers, or those within the Video subsystem. Commands and data to and from the Display subsystem are sent over the Display Control Bus. The REX3 is the master of the Display Control Bus. The second block is the iterator block. This block generates the frame buffer addresses, interpolates the colors and provides masking and various patterning capabilities. The pixel address generation for lines is done by Bresenham iterators. This block also handles the coverage values for anti - aliased lines and does the swizzle for the frame buffer interleaving. The third section is the memory controller and pixel pipe. There are four instances of the memory controller and pixel pipe. This block has the frame buffer controller as well as the CID checking, color compare, dither and Blend functions. The GIO and Iterator sections operate at 33MHz and the memory controller and the pixel pipe operates at 66MHz. The GIO interface with the host is via a fifo which is 64 wide and 32 deep. The high water mark on the GIO fifo is programmable. The Iterator section communicates to the memory controller and pixel pipe via 4 bank fifos. Each bank fifo consists of one write and two read fifos. For screen to screen copy operations the Iterator section generates a read into the read bank fifos and swizzles the data before writing it into the write bank fifos. The memory controller operates each of the 4 banks independent of each other. The memory is cycled in 4 clocks (60nS) for page mode operations. Figure 3 shows the internal data path of REX3.

# 1.6 Performance

| Operation                                 | Performance     |

|-------------------------------------------|-----------------|

| Shaded spans                              | 50M pixels/sec  |

| Flat-filled spans                         | 100M pixels/sec |

| Fastclear                                 | 400M pixels/sec |

| DMA                                       | 50M pixels/sec  |

| Screen to Screen copy                     | 40M pixels/sec  |

| Depthcued or constant color linedraw rate | 20M pixels/sec  |

| 10 pixel RGB Anti-aliased lines           | 200K lines/sec  |

| Random points                             | 6M points/sec   |

Table 1: REX3 Performance

FIGURE 1. Newport Graphics Sub-system

FIGURE 2. REX3 top-level block diagram

FIGURE 3. REX3 Internal Data Path

# 2 Device Interface

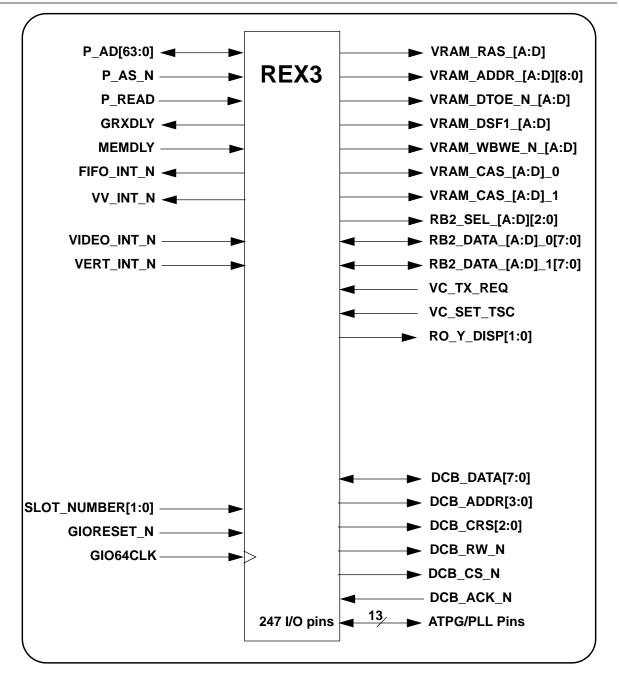

### 2.1 Pin Diagram

### FIGURE 4. REX3 Pin Diagram

### 2.2 Pin Descriptions

The following tables list for each REX3 pin the assertion level, direction (I, O, I/O), LSI IO cell type, followed by a brief functional description.

| Pin Name         | Level | Туре         | Function                                                                                                                                                                                                                                                                                               |

|------------------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_AD[63:0]       | NA    | I/O(BD8TRPU) | 64-bit pipelined Address/data bus                                                                                                                                                                                                                                                                      |

| P_AS_N           | L     | I(TLCHT)     | Asserted during an Address cycle on the GIO bus.                                                                                                                                                                                                                                                       |

| P_READ           | NA    | I(TLCHT)     | Indicates the direction of the data transfer during Address cycles.<br>After the Address cycle, P_READ is driven low to indicate that an<br>active bus cycle is taking place. The GIO64 bus master preempts<br>a transaction by asserting P_READ.                                                      |

| GRXDLY           | Н     | O(BT8RP)     | When asserted, this signal indicates that for read data cycles, the REX3 is not returning valid data on the P_AD bus. For write cycles, the REX3 asserts GRXDLY when the next transfer on the on the non-pipelined side of the GIO64 bus must be stalled (one more word will be accepted by the REX3). |

| MEMDLY           | Η     | I(TLCHT)     | When deasserted during write data cycles, this signal indicates<br>that the host is presenting valid data on the GIO64 bus. When<br>asserted during read data cycles, this signal indicates that the<br>host cannot accept data from the REX3 during the next cycle.                                   |

| FIFO_INT_N       | L     | O(BT4OD)     | REX3 GFIFO/BFIFO above/below interrupt (Open Drain).                                                                                                                                                                                                                                                   |

| VV_INT_N         | L     | O(BT4OD)     | VC2 Vertical retrace or Kaleidoscope Video Option interrupt (Open Drain).                                                                                                                                                                                                                              |

| SLOT_NUMBER[1:0] | NA    | I(TLCHT)     | Address bits [23:22] of the Newport graphics board. Address bits [31:24] = "0001_1111".                                                                                                                                                                                                                |

| GIORESET_N       | L     | I(TLCHT)     | Synchronous reset.                                                                                                                                                                                                                                                                                     |

| GIO64CLK         | NA    | I(CMOS)      | Positive GIO64 bus clock. All GIO64 bus signals are clocked on the rising edge of this signal.                                                                                                                                                                                                         |

#### TABLE 2. GIO64 Bus Interface

### TABLE 3. VRAM/RB2/REORG Interface

| Pin Name              | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VRAM_RAS_[A:D]        | O(B4)        | VRAM RAS, for the four memory banks[A:D]                                                                                                                                                                                                                                                                                                                                                                                          |

| VRAM_ADDR_[A:D][8:0]  | O(BT4RP)     | VRAM Address bus                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VRAM_DTOE_N_[A:D]     | O(BT4RP)     | VRAM Transfer Enable / Output Enable.                                                                                                                                                                                                                                                                                                                                                                                             |

| VRAM_DSF1_[A:D]       | O(BT4RP)     | VRAM special function control pin.                                                                                                                                                                                                                                                                                                                                                                                                |

| VRAM_WBWE_N_[A:D]     | O(B4)        | VRAM bank write enable (active low).                                                                                                                                                                                                                                                                                                                                                                                              |

| VRAM_CAS_[A:D]_0      | O(BT4RP)     | VRAM CAS for the even halves of the four memory banks                                                                                                                                                                                                                                                                                                                                                                             |

| VRAM_CAS_[A:D]_1      | O(BT4RP)     | VRAM CAS for the odd halves of the four memory banks                                                                                                                                                                                                                                                                                                                                                                              |

| RB2_SEL_[A:D][2:0]    | O(B4)        | Operation selects for the four memory banks. Encoded as<br>follows: 000 NOOP<br>001 Write (4 components), lower pixel into OLY planes<br>010 Write higher pixel into OLY planes<br>011 Load write mask and partial DRAWMODE1 Regs<br>100 Read (4 components), lower pixel of OLY planes<br>101 Read higher pixel of OLY planes<br>110 Read lower pixel CID bits (for CID checking)<br>111 Read higher CID bits (for CID checking) |

| RB2_DATA_[A:D]_0[7:0] | I/O(BD8TRPU) | RB2 data for the even halves of the four memory banks                                                                                                                                                                                                                                                                                                                                                                             |

| RB2_DATA_[A:D]_1[7:0] | I/O(BD8TRPU) | RB2 data for the odd halves of the four memory banks                                                                                                                                                                                                                                                                                                                                                                              |

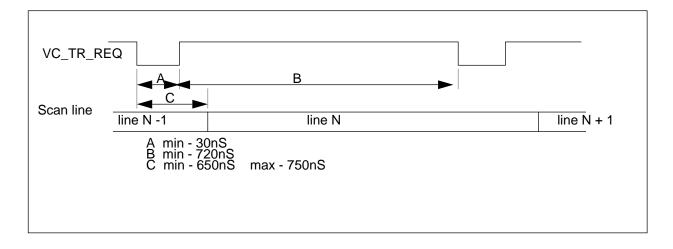

| VC_TX_REQ             | I(TLCHT)     | Transfer request                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VC_SET_TSC            | I(TLCHT)     | Set top of scan.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RO_Y_DISP[1:0]        | O(BT4RP)     | Scanline (modulo-4) for staggering the frame buffer                                                                                                                                                                                                                                                                                                                                                                               |

| Pin Name      | Level | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCB_DATA[7:0] | NA    | I/O(BD8TRPU) | Data read from (DCB_RW_N = 1) or written (DCB_RW_N = 0) to the Display Control Bus slave devices.                                                                                                                                                                                                                                                                                         |

| DCB_ADDR[3:0] | NA    | O(BT4RP)     | Display Control Bus slave device Address.                                                                                                                                                                                                                                                                                                                                                 |

| DCB_CRS[2:0]  | NA    | O(BT8RP)     | Display Control Bus slave device command or register select field.                                                                                                                                                                                                                                                                                                                        |

| DCB_RW_N      | NA    | O(BT8RP)     | Read/Write direction signal.                                                                                                                                                                                                                                                                                                                                                              |

| DCB_CS_N      | NA    | O(BT4RP)     | Display Control Bus command strobe, indicating that valid DCB_ADDR, DCB_CRS, DCB_RW_N and, for write transfers, DCB_DATA are on the bus.                                                                                                                                                                                                                                                  |

| DCB_ACK_N     | L     | I(IBUFN)     | Acknowledge signal for Display Control Bus slaves to handshake transfers with the REX3. When asserted during write cycles, DCB_ACK_N indicates that the slave device has accepted the DCB_DATA, and that the next Display Control Bus cycle may begin. During read cycles, the Display Control Bus slave asserts DCB_ACK to indicate that it has placed valid data on the DCB_DATA lines. |

### TABLE 4. Display Control Bus Interface

#### TABLE 5. Miscellaneous Back-End Pins

| Pin Name    | Level | Туре     | Function                                 |

|-------------|-------|----------|------------------------------------------|

| VERT_INT_N  | L     | I(IBUFN) | Vertical retrace/sync interrupt from VC2 |

| VIDEO_INT_N | L     | I(IBUFN) | Interrupt from Express Video option      |

### TABLE 6. ASIC Mandatory PLL and Test Pins

| Pin Name    | Level | Туре        | Function                                                                                                                                                                                                                                                                                                                      |

|-------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG_TDI    | NA    | I(TLCHTU)   | Scan Test Data In                                                                                                                                                                                                                                                                                                             |

| JTAG_TMS    | NA    | I(TLCHTU)   | Scan Test Mode Select. Selects the scan input of all flip-flops when driven low. Driven high for normal operation.                                                                                                                                                                                                            |

| JTAG_TCK    | NA    | I(TLCHTU)   | Scan Test Clock                                                                                                                                                                                                                                                                                                               |

| JTAG_TDO    | NA    | O(B2)       | Scan Test Data/Parametric NAND tree/PLL Test Clock Out                                                                                                                                                                                                                                                                        |

| TEI         | NA    | I(TLCHN)    | I/O pin tristate enable. When driven low, all bidirectional pins and tri-state unidirectional pins are forced into high impedance state. Driven high for normal operation.                                                                                                                                                    |

| TP[1:0]     | NA    | I(TLCHT)    | PLL/Scan Test Mode. Encoded as follows:<br>00 Normal Operation. VCO ripple counter output -> JTAG_TDO<br>01 PLL bypass mode. Scan chain output -> JTAG_TDO<br>10 PLL bypass mode. Parametric NAND tree -> JTAG_TDO<br>11 Scan mode. JTAG_TCK drives all flops. Scan chain<br>output -> JTAG_TDO. VCO is disabled for IDD test |

| PLL_RESET_N | L     | I(TLCHT)    | PLL Reset. The loop filter output is grounded when asserted                                                                                                                                                                                                                                                                   |

| LP1         | NA    | O(DDRVO)    | PLL Charge Pump Output / Loop Filter Input                                                                                                                                                                                                                                                                                    |

| LP2         | NA    | I/O(RDDRVPD | ) PLL VCO input / Loop Filter Output                                                                                                                                                                                                                                                                                          |

| AVDD        | NA    | I(RDDRV)    | PLL Analog VDD                                                                                                                                                                                                                                                                                                                |

| AVSS        | NA    | I(RDDRV)    | PLL Analog VSS                                                                                                                                                                                                                                                                                                                |

| AGND        | NA    | O(RDDRVO)   | PLL Analog Ground                                                                                                                                                                                                                                                                                                             |

### 2.3 VHDL Description

This section describes the device level interface to the REX3 as a VHDL entity. entitiv REX3 is port( --ĠIO64 Bus interface (74 pins) P\_AD : inout mvl7w\_vector (63 downto 0); P\_AS\_N : in mvl7w; P\_READ : in mvl7w; GRXDLY : out mvl7w; MEMDLY : in mvl7w; FIFO\_INT\_N : out mvl7w; VV INT N : out mvl7w; SLOT NUMBER : in mvl7w vector (1 downto 0); GIORESET\_N : in mvl7w; GIO64CLK : in mvI7w; --VRAM/RB2/REORG Interface (140 pins) VRAM\_RAS\_A: out mvl7w; VRAM\_ADDR\_A : out mvI7w\_vector (8 downto 0); VRAM\_DTOE\_N\_A : out mvl7w; VRAM DSF1 A : out mvl7w: VRAM WBWE N A : out mvl7w; VRAM\_CAS\_A\_0 : out mvl7w; VRAM\_CAS\_A\_1 : out mvl7w; RB2\_SEL\_A : out mvl7w\_vector (2 downto 0); RB2\_DATA\_A\_0 : inout mvl7w\_vector (7 downto 0); RB2\_DATA\_A\_1 : inout mvl7w\_vector (7 downto 0); VRAM RAS B : out mvl7w; VRAM\_ADDR\_B : out mvI7w\_vector (8 downto 0); VRAM\_DTOE\_N\_B : out mvl7w; VRAM DSF1 B : out mvl7w; VRAM WBWE N B : out mvl7w: VRAM CAS B 0: out mvl7w; VRAM\_CAS\_B\_1 : out mvl7w; RB2\_SEL\_B : out mvI7w\_vector (2 downto 0); RB2\_DATA\_B\_0 : inout mvl7w\_vector (7 downto 0); RB2\_DATA\_B\_1: inout mvl7w\_vector (7 downto 0); VRAM\_RAS\_C : out mvl7w; VRAM\_ADDR\_C : out mvl7w\_vector (8 downto 0); VRAM\_DTOE\_N\_C : out mvl7w; VRAM\_DSF1\_C : out mvl7w; VRAM\_WBWE\_N\_C : out mvl7w; VRAM\_CAS\_C\_0 : out mvl7w; VRAM\_CAS\_C\_1 : out mvl7w; RB2\_SEL\_C: out mvl7w\_vector (2 downto 0); RB2\_DATA\_C\_0 : inout mvl7w\_vector (7 downto 0); RB2\_DATA\_C\_1 : inout mvl7w\_vector (7 downto 0); VRAM\_RAS\_D : out mvl7w; VRAM\_ADDR\_D : out mvl7w\_vector (8 downto 0); VRAM DTOE N D : out mvl7w; VRAM DSF1 D : out mvl7w; VRAM\_WBWE\_N\_D : out mvl7w; VRAM\_CAS \_D\_0 : out mvl7w; VRAM\_CAS \_D\_1 : out mvl7w; VRAM\_CAS \_D\_1 : out mvl7w; RB2\_SEL\_D : out mvl7w\_vector (2 downto 0); RB2 DATA D 0 : inout mvl7w vector (7 downto 0); RB2\_DATA\_D\_1 : inout mvI7w\_vector (7 downto 0); VC\_TX\_REQ : in mvl7w; VC SET TSC : in mvl7w;

RO\_Y\_DISP : out mvI7w\_vector (1 downto 0); --Display Control Bus Interface (18 pins) DCB\_ADDR : out mvl7w\_vector (3 downto 0); DCB\_DATA : inout mvl7w\_vector (7 downto 0); DCB\_CRS : out mvl7w\_vector (2 downto 0); DCB\_CS\_N : out mvl7w; DCB RW N : out mvl7w; DCB ACK N : in mvl7w; --Miscellaneous Back End pins (2 pins) VERT\_INT\_N : in mvl7w; VIDEO\_INT\_N : in mvl7w; --ASIC Mandatory pins (13 pins) TEI : in mvl7w; --External tri-state control JTAG\_TDI : in mvl7w; JTAG\_TMS : in mvl7w; JTAG\_TCK : in mvl7w; JTAG\_TCC : out mvl7w; JTAG\_TDO : out mvl7w; TP : in mvl7w vector (1 downto 0); PLL RESET N : in mvl7w; LP1 : out mvl7w; LP2 : in mvl7w; AGND : out mvl7w; AVSS : in mvl7w; AVDD : in mvl7w

end REX3;

### 2.4 Package Pin Assignment

The following list of package pin assignments is from the LSI Logic LBOND program. The REX3 is mounted in a 304 MQUAD cavity down package, and pins are numbered by LSI in a counter-clockwise manner when viewing the die. When mounted (cavity down) on the PC board, pins are also numbered in a counter-clockwise fashion. Therefore, the printed circuit board pin number is equal to (305-LSI pin number).

Pin Number Signal Name

| 27 p_ad_25 | 29         p_ad_27           30         p_ad_28           31         p_ad_29           32         vdd           33         p_ad_30                              |    |      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|

|            | 27         p_ad_25           28         p_ad_26           29         p_ad_27           30         p_ad_28           31         p_ad_29           32         vdd | 25 | avdd |

| $\begin{array}{c} 35\\ 36\\ 37\\ 38\\ 39\\ 40\\ 41\\ 42\\ 43\\ 44\\ 45\\ 46\\ 47\\ 48\\ 49\\ 55\\ 15\\ 25\\ 34\\ 55\\ 56\\ 57\\ 85\\ 96\\ 61\\ 26\\ 36\\ 66\\ 66\\ 66\\ 66\\ 66\\ 66\\ 66\\ 66\\ 6$ | p_as_n<br>p_read<br>p_memdly<br>p_grxdly<br>p_ad_32<br>p_ad_33<br>vdd<br>vss<br>vss<br>p_ad_34<br>p_ad_35<br>p_ad_35<br>p_ad_36<br>p_ad_37<br>p_ad_38<br>vdd<br>p_ad_39<br>p_ad_40<br>p_ad_41<br>p_ad_42<br>p_ad_42<br>p_ad_43<br>vss<br>p_ad_44<br>p_ad_45<br>p_ad_45<br>p_ad_46<br>p_ad_47<br>p_ad_48<br>vdd<br>p_ad_50<br>p_ad_51<br>p_ad_52<br>p_ad_51<br>p_ad_52<br>p_ad_53<br>vss<br>p_ad_54<br>p_ad_55<br>p_ad_55<br>p_ad_55<br>p_ad_56<br>p_ad_57<br>p_ad_58<br>vdd<br>p_ad_61<br>p_ad_61<br>p_ad_62<br>p_ad_63<br>slot_number_0<br>slot_number_0<br>slot_number_0<br>slot_number_0<br>slot_number_1<br>tp_1<br>video_int_n<br>vert_int_n<br>itag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei<br>jtag_tck<br>tei |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 106<br>107<br>108<br>109<br>110                                                                                                                                                                     | rb2_data_a_0_7<br>vram_wbwe_n_a<br>vram_dtoe_n_a<br>vram_dsf1_a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 115<br>116                                                                                                                                                                                          | vram_addr_a_1<br>vram_addr_a_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 117               | vram_addr_a_3                                    |

|-------------------|--------------------------------------------------|

| 118               | vss                                              |

| 119               | vdd                                              |

| 120               | vram_addr_a_4                                    |

| 121               | vram_addr_a_5                                    |

| 122               | vram_addr_a_6                                    |

| 123               | vram_addr_a_7                                    |

| 124               | vram_addr_a_8                                    |

| 125               | vss                                              |

| 126               | vram_ras_a                                       |

| 127               | vram_cas_a_0                                     |

| 128               | vram_cas_a_1                                     |

| 129               | rb2_data_a_1_0                                   |

| 130               | rb2_data_a_1_1                                   |

| 131               | vdd                                              |

| 132               | rb2_data_a_1_2                                   |

| 133               | rb2_data_a_1_3                                   |

| 134               | rb2 data a 1 4                                   |

| 135               | rb2_data_a_1_5                                   |

| 136               | rb2_data_a_1_6                                   |

| 137               | vss                                              |

| 138               | rb2_data_a_1_7                                   |

| 139               | rb2_data_b_0_0                                   |

| 140               | vdd                                              |

| 141               | rb2_data_b_0_1                                   |

| 142               | rb2_data_b_0_2                                   |

| 143               | rb2_data_b_0_3                                   |

| 144               | rb2_data_b_0_4                                   |

| 145<br>146        | rb2_data_b_0_5                                   |

| 140<br>147<br>148 | rb2_data_b_0_6<br>rb2_data_b_0_7                 |

| 149               | vram_wbwe_n_b                                    |

| 150               | vram_dtoe_n_b                                    |

| 151               | vram_dsf1_b                                      |

| 152               | vdd                                              |

| 153               | vss                                              |

| 154               | rb2_sel_b_0                                      |

| 155               | rb2_sel_b_1                                      |

| 156               | rb2_sel_b_2                                      |

| 157               | vram_addr_b_0                                    |

| 158               | vdd                                              |

| 159               | vram addr b 1                                    |

| 160               | vram_addr_b_2                                    |

| 161               | vram_addr_b_3                                    |

| 162               | vram_addr_b_4                                    |

| 163               | vram_addr_b_5                                    |

| 164               | vss                                              |

| 165               | vram_addr_b_6                                    |

| 166               | vram_addr_b_7<br>vram_addr_b_8                   |

| 167<br>168        | vram_ras_b                                       |

| 169               | vram_cas_b_0                                     |

| 170               | vdd                                              |

| 171<br>172        | vram_cas_b_1<br>rb2_data_b_1_0<br>rb2_data_b_1_1 |

| 173               | rb2_data_b_1_1                                   |

| 174               | rb2_data_b_1_2                                   |

| 175               | rb2_data_b_1_3                                   |

| 176               | vss                                              |

| 177               | rb2_data_b_1_4                                   |

| 178               | rb2_data_b_1_5                                   |

| 179               | rb2_data_b_1_6                                   |

| 180               | rb2_data_b_1_7                                   |

| 181               | rb2_data_c_0_0                                   |

| 182               | vdd                                              |

| 183               | rb2_data_c_0_1                                   |

| 184               | rb2_data_c_0_2                                   |

| 185               | rb2_data_c_0_3                                   |

| 186               | rb2_data_c_0_4                                   |

| 187               | rb2_data_c_0_5                                   |

| 188               | vss                                              |

| 189               | rb2_data_c_0_6                                   |

| 190               | rb2_data_c_0_7                                   |

| 190<br>191<br>102 | rb2_data_c_0_7<br>vram_wbwe_n_c                  |

| 192               | vram_dtoe_n_c                                    |

| 193               | vram_dsf1_c                                      |

| 194               | vdd                                              |

| 195               | vss                                              |

| 196               | rb2_sel_c_0                                      |

| 197               | rb2_sel_c_1                                      |

| 198<br>199<br>200 | rb2_sel_c_2<br>vram_addr_c_0   |

|-------------------|--------------------------------|

| 201               | vram_addr_c_1<br>vdd           |

| 202               | vram_addr_c_2                  |

| 203               | vram_addr_c_3                  |

| 204               | vram_addr_c_4                  |

| 205               | vram_addr_c_5                  |

| 206               | vram_addr_c_6                  |

| 207<br>208        | VSS                            |

| 208               | vram_addr_c_7<br>vram_addr_c_8 |

| 210               | vram_ras_c                     |

| 211               | vram_cas_c_0                   |

| 212               | vram_cas_c_1                   |

| 213               | vdd                            |

| 214               | rb2_data_c_1_0                 |

| 215<br>216        | rb2_data_c_1_1                 |

| 217               | rb2_data_c_1_3                 |

| 218               | rb2_data_c_1_4                 |

| 219               | vss                            |

| 220               | rb2 data c 1 5                 |

| 221               | rb2_data_c_1_6                 |

| 222               | rb2_data_c_1_7                 |

| 223               | rb2_data_d_0_0                 |

| 224               | rb2_data_d_0_1                 |

| 225               | vdd                            |

| 226               | rb2_data_d_0_2                 |

| 227               | rb2_data_d_0_3                 |

| 228               | VSS                            |

| 229               | vdd                            |

| 230               | rb2 data d 0 4                 |

| 231               | rb2_data_d_0_5                 |

| 232               | rb2_data_d_0_6                 |

| 233               | rb2_data_d_0_7                 |

| 234               | vram_wbwe_n_d                  |

| 235               | vss                            |

| 236               | vram_dtoe_n_d                  |

| 237               | vram_dsf1_d                    |

| 238               | rb2_sel_d_0                    |

| 239               | rb2_sel_d_1                    |

| 240               | rb2_sel_d_2                    |

| 241               | vdd                            |

| 242               | vram_addr_d_0                  |

| 243               | vram_addr_d_1                  |

| 244               | vram_addr_d_2                  |

| 245               | vram_addr_d_3                  |

| 246               | VSS                            |

| 247               | vram_addr_d_4                  |

| 248               | vram addr d 5                  |

| 249<br>250        | vram_addr_d_6                  |

| 250               | vram_addr_d_7                  |

| 251               | vram_addr_d_8                  |

| 252               | vdd                            |

| 253               | vram ras d                     |

| 254               | vram_cas_d_0                   |

| 255               | vram_cas_d_1                   |

| 256               | rb2_data_d_1_0                 |

| 257               | rb2_data_d_1_1                 |

| 258               | rb2_data_d_1_2                 |

| 259               | VSS                            |

| 260               | rb2_data_d_1_3                 |

| 261               | rb2_data_d_1_4                 |

| 262               | rb2_data_d_1_5                 |

| 263               | rb2 data d 1 6                 |

| 264               | rb2_data_d_1_7                 |

| 265               | vdd                            |

| 266               | vss                            |

| 267               | dcb_data_0                     |

| 268               | dcb_data_1                     |

| 269               | dcb_data_2                     |

| 270               | dcb_data_3                     |

| 271               | dcb_data_4                     |

| 272               | vdd                            |

| 273               | dcb data 5                     |

| 274               | dcb_data_6                     |

| 275               | dcb_data_7                     |

| 276               | dcb_crs_0                      |

| 277               | dcb_crs_1                      |

| 278               | VSS                            |

| 279<br>280<br>281<br>282<br>283<br>284<br>285<br>286<br>287<br>288<br>289<br>290<br>291<br>292<br>293<br>294<br>295<br>296<br>297<br>298<br>299<br>299<br>299<br>300<br>301 | dcb_crs_2<br>dcb_rw_n<br>vdd<br>dcb_cs_n<br>dcb_addr_0<br>dcb_addr_1<br>dcb_addr_2<br>dcb_addr_3<br>vss<br>dcb_ack_n<br>vv_int_n<br>fifo_int_n<br>vss<br>gioreset_n<br>p_ad_0<br>p_ad_1<br>p_ad_2<br>p_ad_3<br>p_ad_4<br>vdd<br>p_ad_5<br>p_ad_6<br>p_ad_7 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 300                                                                                                                                                                         | p_ad_6                                                                                                                                                                                                                                                     |

| 302<br>303                                                                                                                                                                  | p_ad_8<br>p_ad_9                                                                                                                                                                                                                                           |

| 304                                                                                                                                                                         | VSS                                                                                                                                                                                                                                                        |

# 3 **Programmer Interface**

### 3.1 Registers

Table 7 lists the host accessible registers in REX3.

Addresses shown are an offset from the base GIO address of 0x1FnF0000, where n=(0,4,8,C), depending upon the strapping of the GIO64 SLOT\_NUMBER(1:0) pins. Address offsets beginning with 0x1nnn are intended to map corresponding registers into a separate "protected" page.

Access to address + 0x0800 issues primitive GO command.

Type " $\otimes$ " registers are not passed through either BFIFO or GFIFO, and force an immediate action when written to.

Type "0" registers are associated with the Display Control Bus and go through BFIFO.

Registers other than type "⊗" and "◊" are associated with the graphics context and go through GFIFO.

Writes to type "•" registers will stall at the output of GFIFO until the graphics pipeline is idle.

Type "2c" indicates twos-complement value.

Type "sm" indicates signed magnitude value.

Write/Read format bit grouping is shown with location of binary point, (for COLOR registers, 24-bit mode binary point shown). "s" refers to sign bit and "o" refers to overflow bit. Parenthesis are used to indicate a place holder for unused bits.

Write format "#" denotes write-only command address.

Unused bits return 0 when read.

| Address | Name        | Туре | Write     | Read      | Description                                                                                                                                    |

|---------|-------------|------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000  | DRAWMODE1   | •    | 32        | 32        | Draw mode bits.                                                                                                                                |

| 0x0004  | DRAWMODE0   |      | 24        | 24        | Draw instruction and mode bits.                                                                                                                |

| 0x0008  | LSMODE      |      | 28        | 28        | Line stipple mode register.                                                                                                                    |

| 0x000C  | LSPATTERN   |      | 32        | 32        | Line stipple pattern, (msb = first pixel).                                                                                                     |

| 0x0010  | LSPATSAVE   |      | 32        | 32        | Copy of LSPATTERN for pattern restore (LSRESTORE).                                                                                             |

| 0x0014  | ZPATTERN    |      | 32        | 32        | Pattern register, (msb = first pixel).                                                                                                         |

| 0x0018  | COLORBACK   | •    | 32        | 32        | AGBR/CI opaque patterning color or blendfunction destination color.                                                                            |

| 0x001C  | COLORVRAM   | •    | 32        | 32        | VRAM FASTCLEAR color, (set DRAWDEPTH and RGBMODE first).                                                                                       |

| 0x0020  | ALPHAREF    | •    | 8         | 8         | AFUNCTION reference alpha value.                                                                                                               |

| 0x0024  | STALL0      | •    | #         |           | Forces stall at the output of GFIFO until graphics pipeline is idle.                                                                           |

| 0x0028  | SMASK0X     | 2c   | 16,16     | 16,16     | Screenmask 0: min, max boundaries, (window relative GL smask).                                                                                 |

| 0x002C  | SMASK0Y     | 2c   | 16,16     | 16,16     | Screenmask 0: min, max boundaries, (window relative GL smask).                                                                                 |

| 0x0030  | SETUP       |      | #         |           | Performs line/span setup without iteration (ignore DOSETUP).                                                                                   |

| 0x0034  | STEPZ       |      | #         |           | Enables ZPATTERN (Z test fail) for one iteration, (current pixel).                                                                             |

| 0x0038  | LSRESTORE   |      | #         |           | Updates LSPATTERN/LSRCOUNT with LSPATSAVE/LSRCNTSAVE.                                                                                          |

| 0x003C  | LSSAVE      |      | #         |           | Updates LSPATSAVE/LSRCNTSAVE with LSPATTERN/LSRCOUNT.                                                                                          |

| 0x0100  | XSTART      | 2c   | 16.4(7)   | 16.4(7)   | Iterator X start-point (current), full state for context switch.                                                                               |

| 0x0104  | YSTART      | 2c   | 16.4(7)   | 16.4(7)   | Iterator Y start-point (current), full state for context switch.                                                                               |

| 0x0108  | XEND        | 2c   | 16.4(7)   | 16.4(7)   | Iterator X endpoint, full state for context switch.                                                                                            |

| 0x010C  | YEND        | 2c   | 16.4(7)   | 16.4(7)   | Iterator Y endpoint, full state for context switch.                                                                                            |

| 0x0110  | XSAVE       | 2c   | 16        | 16        | Copy of XSTART integer value for BLOCK addressing MODE.                                                                                        |

| 0x0114  | XYMOVE      | 2c • | 16,16     | 16,16     | X,Y offset from XSTART,YSTART for relative operations (Scr2Scr).                                                                               |

| 0x0118  | BRESD       | 2c   | 19.8      | 19.8      | Bresenham "d" error term, for context switch.                                                                                                  |

| 0x011C  | BRESS1      | 2c   | 2.15      | 2.15      | Antialiased Bresenham "s1" coverage term, for context switch.                                                                                  |

| 0x0120  | BRESOCTINC1 |      | 3(4),17.3 | 3(4),17.3 | Bresenham octant & "incr1" error term increment value, for cntx switch.                                                                        |

| 0x0124  | BRESRNDINC2 | 2c   | 8(3),18.3 | 8(3),18.3 | Bresenham 8-bit octant rounding mode (msb == octant 1, lsb == octant 8)<br>& Bresenham "incr2" error term increment value, for context switch. |

| 0x0128  | BRESE1      |      | 1.15      | 1.15      | Bresenham "e1" constant (minor slope) for antialiased line draw.                                                                               |

| 0x012C  | BRESS2      | 2c   | 18.8      | 18.8      | Antialiased Bresenham "s2" coverage term, for context switch.                                                                                  |

| 0x0130  | AWEIGHT0    |      | 8 x 4     | 8 x 4     | First half of 16x4-bit antialiased RGB/CI line weight table.                                                                                   |

| 0x0134  | AWEIGHT1    |      | 8 x 4     | 8 x 4     | Second half of 16x4-bit antialiased RGB/CI line weight table.                                                                                  |

| 0x0138  | XSTARTF     |      | 12.4(7)   |           | GL version of XSTART, (zeros 4 msbs).                                                                                                          |

| 0x013C  | YSTARTF     |      | 12.4(7)   |           | GL version of YSTART, (zeros 4 msbs).                                                                                                          |

| 0x0140  | XENDF       |      | 12.4(7)   |           | GL version of XEND, (zeros 4 msbs).                                                                                                            |

| 0x0144  | YENDF       |      | 12.4(7)   |           | GL version of YEND, (zeros 4 msbs).                                                                                                            |

| 0x0148  | XSTARTI     | 2c   | 16        |           | Integer format for XSTART.                                                                                                                     |